|

| #define | NVME_ID_NS_LBADS(ns) ((ns)->id_ns.lbaf[NVME_ID_NS_FLBAS_INDEX((ns)->id_ns.flbas)].lbads) |

| |

| #define | NVME_ID_NS_LBADS_BYTES(ns) (1 << NVME_ID_NS_LBADS(ns)) |

| |

| #define | NVME_ID_NS_MS(ns) |

| |

| #define | NVME_ID_NS_LBAF_DS(ns, lba_index) (ns->id_ns.lbaf[lba_index].lbads) |

| |

| #define | NVME_ID_NS_LBAF_MS(ns, lba_index) (ns->id_ns.lbaf[lba_index].ms) |

| |

| #define | NVME_MAX_QS PCI_MSIX_FLAGS_QSIZE |

| |

| #define | NVME_MAX_QUEUE_ENTRIES 0xffff |

| |

| #define | NVME_MAX_STRIDE 12 |

| |

| #define | NVME_MAX_NUM_NAMESPACES 256 |

| |

| #define | NVME_MAX_QUEUE_ES 0xf |

| |

| #define | NVME_MIN_CQUEUE_ES 0x4 |

| |

| #define | NVME_MIN_SQUEUE_ES 0x6 |

| |

| #define | NVME_SPARE_THRESHOLD 20 |

| |

| #define | NVME_TEMPERATURE 0x143 |

| |

| #define | NVME_OP_ABORTED 0xff |

| |

| #define | NVME_CAP_MQES(cap) (((cap) >> CAP_MQES_SHIFT) & CAP_MQES_MASK) |

| |

| #define | NVME_CAP_CQR(cap) (((cap) >> CAP_CQR_SHIFT) & CAP_CQR_MASK) |

| |

| #define | NVME_CAP_AMS(cap) (((cap) >> CAP_AMS_SHIFT) & CAP_AMS_MASK) |

| |

| #define | NVME_CAP_TO(cap) (((cap) >> CAP_TO_SHIFT) & CAP_TO_MASK) |

| |

| #define | NVME_CAP_DSTRD(cap) (((cap) >> CAP_DSTRD_SHIFT) & CAP_DSTRD_MASK) |

| |

| #define | NVME_CAP_NSSRS(cap) (((cap) >> CAP_NSSRS_SHIFT) & CAP_NSSRS_MASK) |

| |

| #define | NVME_CAP_CSS(cap) (((cap) >> CAP_CSS_SHIFT) & CAP_CSS_MASK) |

| |

| #define | NVME_CAP_OC12(cap) (((cap) >> CAP_Oc12SHIFT) & CAP_Oc12MASK) |

| |

| #define | NVME_CAP_MPSMIN(cap) (((cap) >> CAP_MPSMIN_SHIFT) & CAP_MPSMIN_MASK) |

| |

| #define | NVME_CAP_MPSMAX(cap) (((cap) >> CAP_MPSMAX_SHIFT) & CAP_MPSMAX_MASK) |

| |

| #define | NVME_CAP_SET_MQES(cap, val) |

| |

| #define | NVME_CAP_SET_CQR(cap, val) |

| |

| #define | NVME_CAP_SET_AMS(cap, val) |

| |

| #define | NVME_CAP_SET_TO(cap, val) |

| |

| #define | NVME_CAP_SET_DSTRD(cap, val) |

| |

| #define | NVME_CAP_SET_NSSRS(cap, val) |

| |

| #define | NVME_CAP_SET_CSS(cap, val) |

| |

| #define | NVME_CAP_SET_OC(cap, val) |

| |

| #define | NVME_CAP_SET_MPSMIN(cap, val) |

| |

| #define | NVME_CAP_SET_MPSMAX(cap, val) |

| |

| #define | NVME_CC_EN(cc) ((cc >> CC_EN_SHIFT) & CC_EN_MASK) |

| |

| #define | NVME_CC_CSS(cc) ((cc >> CC_CSS_SHIFT) & CC_CSS_MASK) |

| |

| #define | NVME_CC_MPS(cc) ((cc >> CC_MPS_SHIFT) & CC_MPS_MASK) |

| |

| #define | NVME_CC_AMS(cc) ((cc >> CC_AMS_SHIFT) & CC_AMS_MASK) |

| |

| #define | NVME_CC_SHN(cc) ((cc >> CC_SHN_SHIFT) & CC_SHN_MASK) |

| |

| #define | NVME_CC_IOSQES(cc) ((cc >> CC_IOSQES_SHIFT) & CC_IOSQES_MASK) |

| |

| #define | NVME_CC_IOCQES(cc) ((cc >> CC_IOCQES_SHIFT) & CC_IOCQES_MASK) |

| |

| #define | NVME_CSTS_RDY(csts) ((csts >> CSTS_RDY_SHIFT) & CSTS_RDY_MASK) |

| |

| #define | NVME_CSTS_CFS(csts) ((csts >> CSTS_CFS_SHIFT) & CSTS_CFS_MASK) |

| |

| #define | NVME_CSTS_SHST(csts) ((csts >> CSTS_SHST_SHIFT) & CSTS_SHST_MASK) |

| |

| #define | NVME_CSTS_NSSRO(csts) ((csts >> CSTS_NSSRO_SHIFT) & CSTS_NSSRO_MASK) |

| |

| #define | NVME_AQA_ASQS(aqa) ((aqa >> AQA_ASQS_SHIFT) & AQA_ASQS_MASK) |

| |

| #define | NVME_AQA_ACQS(aqa) ((aqa >> AQA_ACQS_SHIFT) & AQA_ACQS_MASK) |

| |

| #define | NVME_CMBLOC_BIR(cmbloc) ((cmbloc >> CMBLOC_BIR_SHIFT) & CMBLOC_BIR_MASK) |

| |

| #define | NVME_CMBLOC_OFST(cmbloc) ((cmbloc >> CMBLOC_OFST_SHIFT) & CMBLOC_OFST_MASK) |

| |

| #define | NVME_CMBLOC_SET_BIR(cmbloc, val) |

| |

| #define | NVME_CMBLOC_SET_OFST(cmbloc, val) |

| |

| #define | NVME_CMBSZ_SQS(cmbsz) ((cmbsz >> CMBSZ_SQS_SHIFT) & CMBSZ_SQS_MASK) |

| |

| #define | NVME_CMBSZ_CQS(cmbsz) ((cmbsz >> CMBSZ_CQS_SHIFT) & CMBSZ_CQS_MASK) |

| |

| #define | NVME_CMBSZ_LISTS(cmbsz) ((cmbsz >> CMBSZ_LISTS_SHIFT) & CMBSZ_LISTS_MASK) |

| |

| #define | NVME_CMBSZ_RDS(cmbsz) ((cmbsz >> CMBSZ_RDS_SHIFT) & CMBSZ_RDS_MASK) |

| |

| #define | NVME_CMBSZ_WDS(cmbsz) ((cmbsz >> CMBSZ_WDS_SHIFT) & CMBSZ_WDS_MASK) |

| |

| #define | NVME_CMBSZ_SZU(cmbsz) ((cmbsz >> CMBSZ_SZU_SHIFT) & CMBSZ_SZU_MASK) |

| |

| #define | NVME_CMBSZ_SZ(cmbsz) ((cmbsz >> CMBSZ_SZ_SHIFT) & CMBSZ_SZ_MASK) |

| |

| #define | NVME_CMBSZ_SET_SQS(cmbsz, val) |

| |

| #define | NVME_CMBSZ_SET_CQS(cmbsz, val) |

| |

| #define | NVME_CMBSZ_SET_LISTS(cmbsz, val) |

| |

| #define | NVME_CMBSZ_SET_RDS(cmbsz, val) |

| |

| #define | NVME_CMBSZ_SET_WDS(cmbsz, val) |

| |

| #define | NVME_CMBSZ_SET_SZU(cmbsz, val) |

| |

| #define | NVME_CMBSZ_SET_SZ(cmbsz, val) |

| |

| #define | NVME_CMBSZ_GETSIZE(cmbsz) (NVME_CMBSZ_SZ(cmbsz) * (1<<(12+4*NVME_CMBSZ_SZU(cmbsz)))) |

| |

| #define | NVME_SGL_TYPE(type) ((type >> 4) & 0xf) |

| |

| #define | NVME_SGL_SUBTYPE(type) (type & 0xf) |

| |

| #define | NVME_CMD_FLAGS_FUSE(flags) (flags & 0x3) |

| |

| #define | NVME_CMD_FLAGS_PSDT(flags) ((flags >> 6) & 0x3) |

| |

| #define | NVME_CQ_FLAGS_PC(cq_flags) (cq_flags & 0x1) |

| |

| #define | NVME_CQ_FLAGS_IEN(cq_flags) ((cq_flags >> 1) & 0x1) |

| |

| #define | NVME_SQ_FLAGS_PC(sq_flags) (sq_flags & 0x1) |

| |

| #define | NVME_SQ_FLAGS_QPRIO(sq_flags) ((sq_flags >> 1) & 0x3) |

| |

| #define | NVME_SET_CSI(vec, csi) (vec |= (uint8_t)(1 << (csi))) |

| |

| #define | NVME_IDENTIFY_DATA_SIZE 4096 |

| |

| #define | NVME_CTRL_SQES_MIN(sqes) ((sqes) & 0xf) |

| |

| #define | NVME_CTRL_SQES_MAX(sqes) (((sqes) >> 4) & 0xf) |

| |

| #define | NVME_CTRL_CQES_MIN(cqes) ((cqes) & 0xf) |

| |

| #define | NVME_CTRL_CQES_MAX(cqes) (((cqes) >> 4) & 0xf) |

| |

| #define | NVME_ARB_AB(arb) (arb & 0x7) |

| |

| #define | NVME_ARB_LPW(arb) ((arb >> 8) & 0xff) |

| |

| #define | NVME_ARB_MPW(arb) ((arb >> 16) & 0xff) |

| |

| #define | NVME_ARB_HPW(arb) ((arb >> 24) & 0xff) |

| |

| #define | NVME_INTC_THR(intc) (intc & 0xff) |

| |

| #define | NVME_INTC_TIME(intc) ((intc >> 8) & 0xff) |

| |

| #define | NVME_ERR_REC_DULBE(err_rec) (err_rec & 0x10000) |

| |

| #define | NVME_NSID_BROADCAST 0xffffffff |

| |

| #define | NVME_ID_NS_NSFEAT_THIN(nsfeat) ((nsfeat & 0x1)) |

| |

| #define | NVME_ID_NS_FLBAS_EXTENDED(flbas) ((flbas >> 4) & 0x1) |

| |

| #define | NVME_ID_NS_FLBAS_INDEX(flbas) ((flbas & 0xf)) |

| |

| #define | NVME_ID_NS_MC_SEPARATE(mc) ((mc >> 1) & 0x1) |

| |

| #define | NVME_ID_NS_MC_EXTENDED(mc) ((mc & 0x1)) |

| |

| #define | NVME_ID_NS_DPC_LAST_EIGHT(dpc) ((dpc >> 4) & 0x1) |

| |

| #define | NVME_ID_NS_DPC_FIRST_EIGHT(dpc) ((dpc >> 3) & 0x1) |

| |

| #define | NVME_ID_NS_DPC_TYPE_3(dpc) ((dpc >> 2) & 0x1) |

| |

| #define | NVME_ID_NS_DPC_TYPE_2(dpc) ((dpc >> 1) & 0x1) |

| |

| #define | NVME_ID_NS_DPC_TYPE_1(dpc) ((dpc & 0x1)) |

| |

| #define | NVME_ID_NS_DPC_TYPE_MASK 0x7 |

| |

| #define | TYPE_NVME "femu" |

| |

| #define | FEMU(obj) OBJECT_CHECK(FemuCtrl, (obj), TYPE_NVME) |

| |

| #define | FEMU_MAX_NUM_CHNLS (32) |

| |

| #define | FEMU_MAX_NUM_CHIPS (128) |

| |

| #define | SQ_POLLING_PERIOD_NS (5000) |

| |

| #define | CQ_POLLING_PERIOD_NS (5000) |

| |

| #define | FEMU_MAX_INF_REQS (65536) |

| |

| #define | MN_MAX_LEN (64) |

| |

| #define | ID_MAX_LEN (4) |

| |

| #define | femu_debug(fmt, ...) do { } while (0) |

| |

| #define | femu_err(fmt, ...) do { fprintf(stderr, "[FEMU] Err: " fmt, ## __VA_ARGS__); } while (0) |

| |

| #define | femu_log(fmt, ...) do { printf("[FEMU] Log: " fmt, ## __VA_ARGS__); } while (0) |

| |

|

| enum | NvmeCapShift {

CAP_MQES_SHIFT = 0,

CAP_CQR_SHIFT = 16,

CAP_AMS_SHIFT = 17,

CAP_TO_SHIFT = 24,

CAP_DSTRD_SHIFT = 32,

CAP_NSSRS_SHIFT = 33,

CAP_CSS_SHIFT = 37,

CAP_OC_SHIFT = 44,

CAP_MPSMIN_SHIFT = 48,

CAP_MPSMAX_SHIFT = 52

} |

| |

| enum | NvmeCapMask {

CAP_MQES_MASK = 0xffff,

CAP_CQR_MASK = 0x1,

CAP_AMS_MASK = 0x3,

CAP_TO_MASK = 0xff,

CAP_DSTRD_MASK = 0xf,

CAP_NSSRS_MASK = 0x1,

CAP_CSS_MASK = 0xff,

CAP_OC_MASK = 0x1,

CAP_MPSMIN_MASK = 0xf,

CAP_MPSMAX_MASK = 0xf

} |

| |

| enum | NvmeCsi { NVME_CSI_NVM = 0x00,

NVME_CSI_ZONED = 0x02

} |

| |

| enum | NvmeCapCss { NVME_CAP_CSS_NVM = 1 << 0,

NVME_CAP_CSS_CSI_SUPP = 1 << 6,

NVME_CAP_CSS_ADMIN_ONLY = 1 << 7

} |

| |

| enum | NvmeCcShift {

CC_EN_SHIFT = 0,

CC_CSS_SHIFT = 4,

CC_MPS_SHIFT = 7,

CC_AMS_SHIFT = 11,

CC_SHN_SHIFT = 14,

CC_IOSQES_SHIFT = 16,

CC_IOCQES_SHIFT = 20

} |

| |

| enum | NvmeCcMask {

CC_EN_MASK = 0x1,

CC_CSS_MASK = 0x7,

CC_MPS_MASK = 0xf,

CC_AMS_MASK = 0x7,

CC_SHN_MASK = 0x3,

CC_IOSQES_MASK = 0xf,

CC_IOCQES_MASK = 0xf

} |

| |

| enum | NvmeCcCss { NVME_CC_CSS_NVM = 0x0,

NVME_CC_CSS_CSI = 0x6,

NVME_CC_CSS_ADMIN_ONLY = 0x7

} |

| |

| enum | NvmeCstsShift { CSTS_RDY_SHIFT = 0,

CSTS_CFS_SHIFT = 1,

CSTS_SHST_SHIFT = 2,

CSTS_NSSRO_SHIFT = 4

} |

| |

| enum | NvmeCstsMask { CSTS_RDY_MASK = 0x1,

CSTS_CFS_MASK = 0x1,

CSTS_SHST_MASK = 0x3,

CSTS_NSSRO_MASK = 0x1

} |

| |

| enum | NvmeCsts {

NVME_CSTS_READY = 1 << CSTS_RDY_SHIFT,

NVME_CSTS_FAILED = 1 << CSTS_CFS_SHIFT,

NVME_CSTS_SHST_NORMAL = 0 << CSTS_SHST_SHIFT,

NVME_CSTS_SHST_PROGRESS = 1 << CSTS_SHST_SHIFT,

NVME_CSTS_SHST_COMPLETE = 2 << CSTS_SHST_SHIFT,

NVME_CSTS_NSSRO = 1 << CSTS_NSSRO_SHIFT

} |

| |

| enum | NvmeAqaShift { AQA_ASQS_SHIFT = 0,

AQA_ACQS_SHIFT = 16

} |

| |

| enum | NvmeAqaMask { AQA_ASQS_MASK = 0xfff,

AQA_ACQS_MASK = 0xfff

} |

| |

| enum | NvmeCmblocShift { CMBLOC_BIR_SHIFT = 0,

CMBLOC_OFST_SHIFT = 12

} |

| |

| enum | NvmeCmblocMask { CMBLOC_BIR_MASK = 0x7,

CMBLOC_OFST_MASK = 0xfffff

} |

| |

| enum | NvmeCmbszShift {

CMBSZ_SQS_SHIFT = 0,

CMBSZ_CQS_SHIFT = 1,

CMBSZ_LISTS_SHIFT = 2,

CMBSZ_RDS_SHIFT = 3,

CMBSZ_WDS_SHIFT = 4,

CMBSZ_SZU_SHIFT = 8,

CMBSZ_SZ_SHIFT = 12

} |

| |

| enum | NvmeCmbszMask {

CMBSZ_SQS_MASK = 0x1,

CMBSZ_CQS_MASK = 0x1,

CMBSZ_LISTS_MASK = 0x1,

CMBSZ_RDS_MASK = 0x1,

CMBSZ_WDS_MASK = 0x1,

CMBSZ_SZU_MASK = 0xf,

CMBSZ_SZ_MASK = 0xfffff

} |

| |

| enum | NvmePsdt { NVME_PSDT_PRP = 0x0,

NVME_PSDT_SGL_MPTR_CONTIGUOUS = 0x1,

NVME_PSDT_SGL_MPTR_SGL = 0x2

} |

| |

| enum | NvmeAdminCommands {

NVME_ADM_CMD_DELETE_SQ = 0x00,

NVME_ADM_CMD_CREATE_SQ = 0x01,

NVME_ADM_CMD_GET_LOG_PAGE = 0x02,

NVME_ADM_CMD_DELETE_CQ = 0x04,

NVME_ADM_CMD_CREATE_CQ = 0x05,

NVME_ADM_CMD_IDENTIFY = 0x06,

NVME_ADM_CMD_ABORT = 0x08,

NVME_ADM_CMD_SET_FEATURES = 0x09,

NVME_ADM_CMD_GET_FEATURES = 0x0a,

NVME_ADM_CMD_ASYNC_EV_REQ = 0x0c,

NVME_ADM_CMD_ACTIVATE_FW = 0x10,

NVME_ADM_CMD_DOWNLOAD_FW = 0x11,

NVME_ADM_CMD_FORMAT_NVM = 0x80,

NVME_ADM_CMD_SECURITY_SEND = 0x81,

NVME_ADM_CMD_SECURITY_RECV = 0x82,

NVME_ADM_CMD_SET_DB_MEMORY = 0x7c,

NVME_ADM_CMD_FEMU_DEBUG = 0xee,

NVME_ADM_CMD_FEMU_FLIP = 0xef

} |

| |

| enum | NvmeIoCommands {

NVME_CMD_FLUSH = 0x00,

NVME_CMD_WRITE = 0x01,

NVME_CMD_READ = 0x02,

NVME_CMD_WRITE_UNCOR = 0x04,

NVME_CMD_COMPARE = 0x05,

NVME_CMD_WRITE_ZEROES = 0x08,

NVME_CMD_DSM = 0x09,

NVME_CMD_ZONE_MGMT_SEND = 0x79,

NVME_CMD_ZONE_MGMT_RECV = 0x7a,

NVME_CMD_ZONE_APPEND = 0x7d,

NVME_CMD_OC_ERASE = 0x90,

NVME_CMD_OC_WRITE = 0x91,

NVME_CMD_OC_READ = 0x92

} |

| |

| enum | NvmeQueueFlags {

NVME_Q_PC = 1,

NVME_Q_PRIO_URGENT = 0,

NVME_Q_PRIO_HIGH = 1,

NVME_Q_PRIO_NORMAL = 2,

NVME_Q_PRIO_LOW = 3

} |

| |

| enum | {

NVME_RW_LR = 1 << 15,

NVME_RW_FUA = 1 << 14,

NVME_RW_DSM_FREQ_UNSPEC = 0,

NVME_RW_DSM_FREQ_TYPICAL = 1,

NVME_RW_DSM_FREQ_RARE = 2,

NVME_RW_DSM_FREQ_READS = 3,

NVME_RW_DSM_FREQ_WRITES = 4,

NVME_RW_DSM_FREQ_RW = 5,

NVME_RW_DSM_FREQ_ONCE = 6,

NVME_RW_DSM_FREQ_PREFETCH = 7,

NVME_RW_DSM_FREQ_TEMP = 8,

NVME_RW_DSM_LATENCY_NONE = 0 << 4,

NVME_RW_DSM_LATENCY_IDLE = 1 << 4,

NVME_RW_DSM_LATENCY_NORM = 2 << 4,

NVME_RW_DSM_LATENCY_LOW = 3 << 4,

NVME_RW_DSM_SEQ_REQ = 1 << 6,

NVME_RW_DSM_COMPRESSED = 1 << 7,

NVME_RW_PRINFO_PRACT = 1 << 13,

NVME_RW_PRINFO_PRCHK_GUARD = 1 << 12,

NVME_RW_PRINFO_PRCHK_APP = 1 << 11,

NVME_RW_PRINFO_PRCHK_REF = 1 << 10

} |

| |

| enum | { NVME_DSMGMT_IDR = 1 << 0,

NVME_DSMGMT_IDW = 1 << 1,

NVME_DSMGMT_AD = 1 << 2

} |

| |

| enum | NvmeAsyncEventRequest {

NVME_AER_TYPE_ERROR = 0,

NVME_AER_TYPE_SMART = 1,

NVME_AER_TYPE_IO_SPECIFIC = 6,

NVME_AER_TYPE_VENDOR_SPECIFIC = 7,

NVME_AER_INFO_ERR_INVALID_SQ = 0,

NVME_AER_INFO_ERR_INVALID_DB = 1,

NVME_AER_INFO_ERR_DIAG_FAIL = 2,

NVME_AER_INFO_ERR_PERS_INTERNAL_ERR = 3,

NVME_AER_INFO_ERR_TRANS_INTERNAL_ERR = 4,

NVME_AER_INFO_ERR_FW_IMG_LOAD_ERR = 5,

NVME_AER_INFO_SMART_RELIABILITY = 0,

NVME_AER_INFO_SMART_TEMP_THRESH = 1,

NVME_AER_INFO_SMART_SPARE_THRESH = 2

} |

| |

| enum | NvmeStatusCodes {

NVME_SUCCESS = 0x0000,

NVME_INVALID_OPCODE = 0x0001,

NVME_INVALID_FIELD = 0x0002,

NVME_CID_CONFLICT = 0x0003,

NVME_DATA_TRAS_ERROR = 0x0004,

NVME_POWER_LOSS_ABORT = 0x0005,

NVME_INTERNAL_DEV_ERROR = 0x0006,

NVME_CMD_ABORT_REQ = 0x0007,

NVME_CMD_ABORT_SQ_DEL = 0x0008,

NVME_CMD_ABORT_FAILED_FUSE = 0x0009,

NVME_CMD_ABORT_MISSING_FUSE = 0x000a,

NVME_INVALID_NSID = 0x000b,

NVME_CMD_SEQ_ERROR = 0x000c,

NVME_INVALID_CMD_SET = 0x002c,

NVME_LBA_RANGE = 0x0080,

NVME_CAP_EXCEEDED = 0x0081,

NVME_NS_NOT_READY = 0x0082,

NVME_NS_RESV_CONFLICT = 0x0083,

NVME_INVALID_CQID = 0x0100,

NVME_INVALID_QID = 0x0101,

NVME_MAX_QSIZE_EXCEEDED = 0x0102,

NVME_ACL_EXCEEDED = 0x0103,

NVME_RESERVED = 0x0104,

NVME_AER_LIMIT_EXCEEDED = 0x0105,

NVME_INVALID_FW_SLOT = 0x0106,

NVME_INVALID_FW_IMAGE = 0x0107,

NVME_INVALID_IRQ_VECTOR = 0x0108,

NVME_INVALID_LOG_ID = 0x0109,

NVME_INVALID_FORMAT = 0x010a,

NVME_FW_REQ_RESET = 0x010b,

NVME_INVALID_QUEUE_DEL = 0x010c,

NVME_FID_NOT_SAVEABLE = 0x010d,

NVME_FID_NOT_NSID_SPEC = 0x010f,

NVME_FW_REQ_SUSYSTEM_RESET = 0x0110,

NVME_CONFLICTING_ATTRS = 0x0180,

NVME_INVALID_PROT_INFO = 0x0181,

NVME_WRITE_TO_RO = 0x0182,

NVME_ZONE_BOUNDARY_ERROR = 0x01b8,

NVME_ZONE_FULL = 0x01b9,

NVME_ZONE_READ_ONLY = 0x01ba,

NVME_ZONE_OFFLINE = 0x01bb,

NVME_ZONE_INVALID_WRITE = 0x01bc,

NVME_ZONE_TOO_MANY_ACTIVE = 0x01bd,

NVME_ZONE_TOO_MANY_OPEN = 0x01be,

NVME_ZONE_INVAL_TRANSITION = 0x01bf,

NVME_INVALID_MEMORY_ADDRESS = 0x01C0,

NVME_WRITE_FAULT = 0x0280,

NVME_UNRECOVERED_READ = 0x0281,

NVME_E2E_GUARD_ERROR = 0x0282,

NVME_E2E_APP_ERROR = 0x0283,

NVME_E2E_REF_ERROR = 0x0284,

NVME_CMP_FAILURE = 0x0285,

NVME_ACCESS_DENIED = 0x0286,

NVME_DULB = 0x0287,

NVME_MORE = 0x2000,

NVME_DNR = 0x4000,

NVME_NO_COMPLETE = 0xffff

} |

| |

| enum | NvmeSmartWarn {

NVME_SMART_SPARE = 1 << 0,

NVME_SMART_TEMPERATURE = 1 << 1,

NVME_SMART_RELIABILITY = 1 << 2,

NVME_SMART_MEDIA_READ_ONLY = 1 << 3,

NVME_SMART_FAILED_VOLATILE_MEDIA = 1 << 4

} |

| |

| enum | {

NVME_CMD_EFF_CSUPP = 1 << 0,

NVME_CMD_EFF_LBCC = 1 << 1,

NVME_CMD_EFF_NCC = 1 << 2,

NVME_CMD_EFF_NIC = 1 << 3,

NVME_CMD_EFF_CCC = 1 << 4,

NVME_CMD_EFF_CSE_MASK = 3 << 16,

NVME_CMD_EFF_UUID_SEL = 1 << 19

} |

| |

| enum | LogIdentifier { NVME_LOG_ERROR_INFO = 0x01,

NVME_LOG_SMART_INFO = 0x02,

NVME_LOG_FW_SLOT_INFO = 0x03,

NVME_LOG_CMD_EFFECTS = 0x05

} |

| |

| enum | NvmeIdCns {

NVME_ID_CNS_NS = 0x00,

NVME_ID_CNS_CTRL = 0x01,

NVME_ID_CNS_NS_ACTIVE_LIST = 0x02,

NVME_ID_CNS_NS_DESCR_LIST = 0x03,

NVME_ID_CNS_CS_NS = 0x05,

NVME_ID_CNS_CS_CTRL = 0x06,

NVME_ID_CNS_CS_NS_ACTIVE_LIST = 0x07,

NVME_ID_CNS_NS_PRESENT_LIST = 0x10,

NVME_ID_CNS_NS_PRESENT = 0x11,

NVME_ID_CNS_CS_NS_PRESENT_LIST = 0x1a,

NVME_ID_CNS_CS_NS_PRESENT = 0x1b,

NVME_ID_CNS_IO_COMMAND_SET = 0x1c

} |

| |

| enum | NvmeIdCtrlOacs {

NVME_OACS_SECURITY = 1 << 0,

NVME_OACS_FORMAT = 1 << 1,

NVME_OACS_FW = 1 << 2,

NVME_OACS_Oc12DEV = 1 << 3,

NVME_OACS_DBBUF = 1 << 8

} |

| |

| enum | NvmeIdCtrlOncs {

NVME_ONCS_COMPARE = 1 << 0,

NVME_ONCS_WRITE_UNCORR = 1 << 1,

NVME_ONCS_DSM = 1 << 2,

NVME_ONCS_WRITE_ZEROS = 1 << 3,

NVME_ONCS_FEATURES = 1 << 4,

NVME_ONCS_RESRVATIONS = 1 << 5

} |

| |

| enum | NvmeIdCtrlFrmw { NVME_FRMW_SLOT1_RO = 1 << 0

} |

| |

| enum | NvmeIdCtrlLpa { NVME_LPA_NS_SMART = 1 << 0,

NVME_LPA_CSE = 1 << 1,

NVME_LPA_EXTENDED = 1 << 2

} |

| |

| enum | NvmeFeatureIds {

NVME_ARBITRATION = 0x1,

NVME_POWER_MANAGEMENT = 0x2,

NVME_LBA_RANGE_TYPE = 0x3,

NVME_TEMPERATURE_THRESHOLD = 0x4,

NVME_ERROR_RECOVERY = 0x5,

NVME_VOLATILE_WRITE_CACHE = 0x6,

NVME_NUMBER_OF_QUEUES = 0x7,

NVME_INTERRUPT_COALESCING = 0x8,

NVME_INTERRUPT_VECTOR_CONF = 0x9,

NVME_WRITE_ATOMICITY = 0xa,

NVME_ASYNCHRONOUS_EVENT_CONF = 0xb,

NVME_TIMESTAMP = 0xe,

NVME_SOFTWARE_PROGRESS_MARKER = 0x80,

NVME_FID_MAX = 0x100

} |

| |

| enum | NvmeFeatureCap { NVME_FEAT_CAP_SAVE = 1 << 0,

NVME_FEAT_CAP_NS = 1 << 1,

NVME_FEAT_CAP_CHANGE = 1 << 2

} |

| |

| enum | NvmeGetFeatureSelect { NVME_GETFEAT_SELECT_CURRENT = 0x0,

NVME_GETFEAT_SELECT_DEFAULT = 0x1,

NVME_GETFEAT_SELECT_SAVED = 0x2,

NVME_GETFEAT_SELECT_CAP = 0x3

} |

| |

| enum | NvmeNsIdentifierLength { NVME_NIDL_EUI64 = 8,

NVME_NIDL_NGUID = 16,

NVME_NIDL_UUID = 16,

NVME_NIDL_CSI = 1

} |

| |

| enum | NvmeNsIdentifierType { NVME_NIDT_EUI64 = 0x01,

NVME_NIDT_NGUID = 0x02,

NVME_NIDT_UUID = 0x03,

NVME_NIDT_CSI = 0x04

} |

| |

| enum | NvmeIdNsDps {

DPS_TYPE_NONE = 0,

DPS_TYPE_1 = 1,

DPS_TYPE_2 = 2,

DPS_TYPE_3 = 3,

DPS_TYPE_MASK = 0x7,

DPS_FIRST_EIGHT = 8

} |

| |

| enum | {

FEMU_OCSSD_MODE = 0,

FEMU_BBSSD_MODE = 1,

FEMU_NOSSD_MODE = 2,

FEMU_ZNSSD_MODE = 3,

FEMU_SMARTSSD_MODE,

FEMU_KVSSD_MODE

} |

| |

| enum | { OCSSD12 = 0x1,

OCSSD20 = 0x2

} |

| |

| enum | OC20AdminCommands { OC20_ADM_CMD_IDENTIFY = 0xe2,

OC20_ADM_CMD_SET_LOG_PAGE = 0xc1

} |

| |

|

| static void | nvme_check_size (void) |

| |

| static bool | OCSSD (FemuCtrl *n) |

| |

| static bool | BBSSD (FemuCtrl *n) |

| |

| static bool | NOSSD (FemuCtrl *n) |

| |

| static bool | ZNSSD (FemuCtrl *n) |

| |

| int | nvme_check_sqid (FemuCtrl *n, uint16_t sqid) |

| |

| int | nvme_check_cqid (FemuCtrl *n, uint16_t cqid) |

| |

| void | nvme_inc_cq_tail (NvmeCQueue *cq) |

| |

| void | nvme_inc_sq_head (NvmeSQueue *sq) |

| |

| void | nvme_update_cq_head (NvmeCQueue *cq) |

| |

| uint8_t | nvme_cq_full (NvmeCQueue *cq) |

| |

| uint8_t | nvme_sq_empty (NvmeSQueue *sq) |

| |

| void | nvme_update_sq_tail (NvmeSQueue *sq) |

| |

| uint16_t | nvme_init_sq (NvmeSQueue *sq, FemuCtrl *n, uint64_t dma_addr, uint16_t sqid, uint16_t cqid, uint16_t size, enum NvmeQueueFlags prio, int contig) |

| | 初始化sq队列,预分配空间 更多...

|

| |

| void | nvme_free_sq (NvmeSQueue *sq, FemuCtrl *n) |

| |

| void | nvme_free_cq (NvmeCQueue *cq, FemuCtrl *n) |

| |

| uint16_t | nvme_init_cq (NvmeCQueue *cq, FemuCtrl *n, uint64_t dma_addr, uint16_t cqid, uint16_t vector, uint16_t size, uint16_t irq_enabled, int contig) |

| |

| void | nvme_set_ctrl_name (FemuCtrl *n, const char *mn, const char *sn, int *dev_id) |

| |

| void | nvme_isr_notify_admin (void *opaque) |

| | 通知上层admin命令已完成 更多...

|

| |

| void | nvme_isr_notify_io (void *opaque) |

| | 中断通知上层取cq 更多...

|

| |

| int | nvme_setup_virq (FemuCtrl *n, NvmeCQueue *cq) |

| |

| int | nvme_clear_virq (FemuCtrl *n) |

| |

| void | nvme_addr_read (FemuCtrl *n, hwaddr addr, void *buf, int size) |

| |

| void | nvme_addr_write (FemuCtrl *n, hwaddr addr, void *buf, int size) |

| |

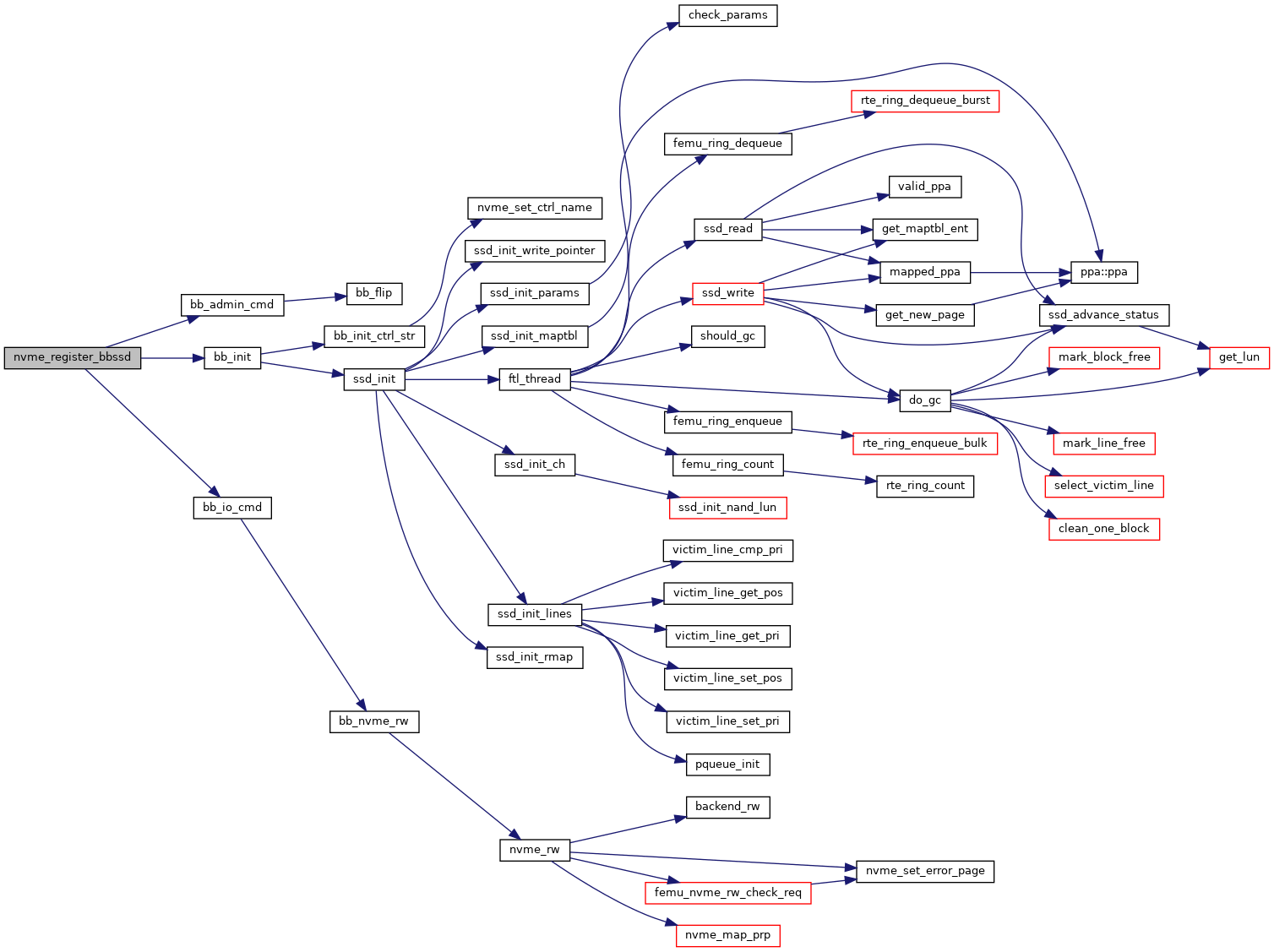

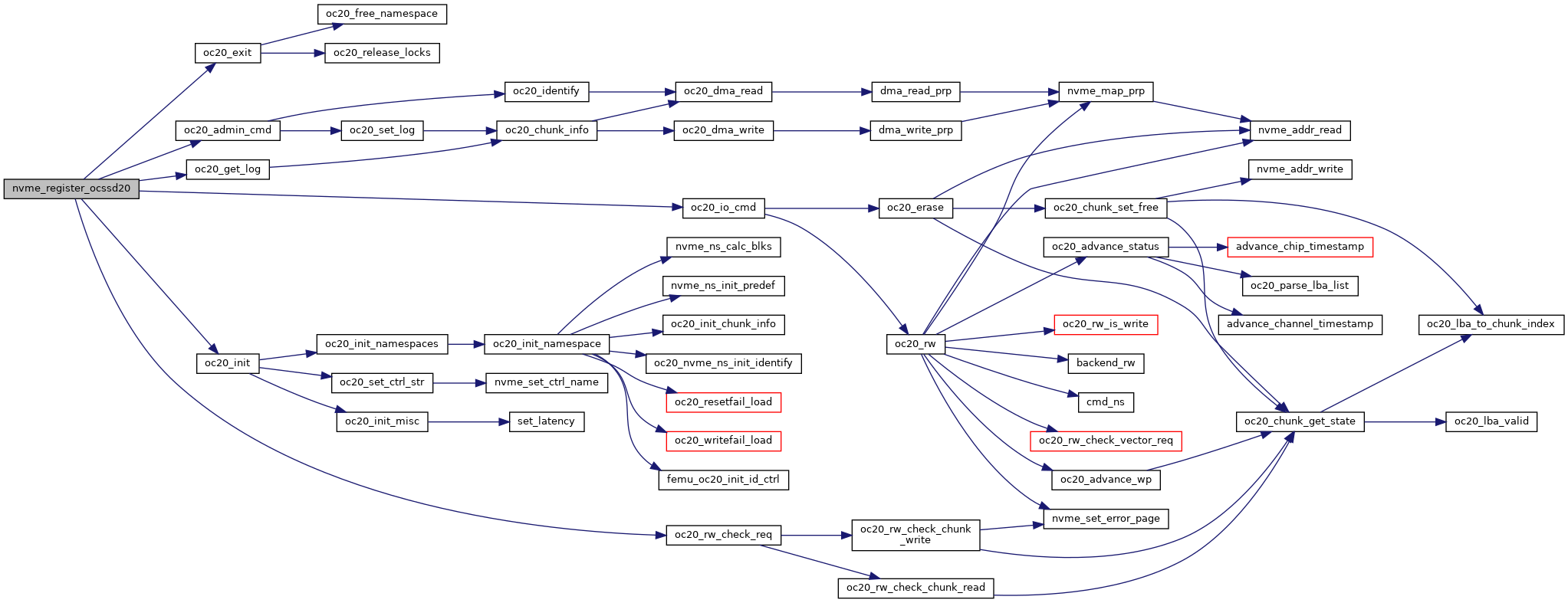

| uint16_t | nvme_map_prp (QEMUSGList *qsg, QEMUIOVector *iov, uint64_t prp1, uint64_t prp2, uint32_t len, FemuCtrl *n) |

| |

| uint16_t | dma_write_prp (FemuCtrl *n, uint8_t *ptr, uint32_t len, uint64_t prp1, uint64_t prp2) |

| |

| uint16_t | dma_read_prp (FemuCtrl *n, uint8_t *ptr, uint32_t len, uint64_t prp1, uint64_t prp2) |

| |

| uint64_t * | nvme_setup_discontig (FemuCtrl *n, uint64_t prp_addr, uint16_t queue_depth, uint16_t entry_size) |

| |

| void | nvme_set_error_page (FemuCtrl *n, uint16_t sqid, uint16_t cid, uint16_t status, uint16_t location, uint64_t lba, uint32_t nsid) |

| |

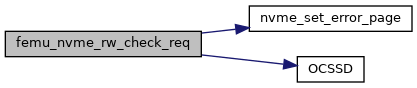

| uint16_t | femu_nvme_rw_check_req (FemuCtrl *n, NvmeNamespace *ns, NvmeCmd *cmd, NvmeRequest *req, uint64_t slba, uint64_t elba, uint32_t nlb, uint16_t ctrl, uint64_t data_size, uint64_t meta_size) |

| |

| void | nvme_process_sq_admin (void *opaque) |

| | 处理admin命令的sq队列 更多...

|

| |

| void | nvme_post_cqes_io (void *opaque) |

| | 将剩余的req都填入cq 更多...

|

| |

| void | nvme_create_poller (FemuCtrl *n) |

| | 创建poller线程,以及两个ring queue:to_ftl和to_poller 更多...

|

| |

| uint16_t | nvme_rw (FemuCtrl *n, NvmeNamespace *ns, NvmeCmd *cmd, NvmeRequest *req) |

| | nvme读写命令 更多...

|

| |

| int | nvme_register_ocssd12 (FemuCtrl *n) |

| |

| int | nvme_register_ocssd20 (FemuCtrl *n) |

| |

| int | nvme_register_nossd (FemuCtrl *n) |

| |

| int | nvme_register_bbssd (FemuCtrl *n) |

| | 注册blackbox相关函数 更多...

|

| |

| int | nvme_register_znssd (FemuCtrl *n) |

| |

| static uint64_t | ns_blks (NvmeNamespace *ns, uint8_t lba_idx) |

| |

| static hwaddr | nvme_discontig (uint64_t *dma_addr, uint16_t page_size, uint16_t queue_idx, uint16_t entry_size) |

| | 地址不连续时取cmd地址 更多...

|

| |

| static uint16_t | nvme_check_mdts (FemuCtrl *n, size_t len) |

| |